当单片机所有多余的地址线都接到译码器的信号输入端时,这种译码方式称为()。A、线译码B、部分译码C、全译码D、混合译码

题目

当单片机所有多余的地址线都接到译码器的信号输入端时,这种译码方式称为()。

- A、线译码

- B、部分译码

- C、全译码

- D、混合译码

参考答案和解析

相似问题和答案

第1题:

译码器哪个输出信号有效取决于译码器的地址输入信号。()

第2题:

第3题:

此题为判断题(对,错)。

第4题:

在现行PC机中,常用存储器地址线中的低10位作输入输出口地址线。设某接口芯片内部有16个端口,该接口芯片的片选信号由地址译码器产生,则地址译码器的输入地址线一般应为( )。

A.其中的高8位地址线

B.其中的高4位地址线,

C.其中的高6位地址线

D.以上都不对

第5题:

在现行PC机中,常用存储器地址线中的低10位作输入/输出口地址线。设某接口芯片内部有16个端口,该接口芯片的片选信号由地址译码器产生,则地址译码器的输入地址线一般应为( )。

A.全部10位地址线

B.其中的高8位地址线

C.其中的高6位地址线

D.其中的高4位地址线

第6题:

此题为判断题(对,错)。

第7题:

A.0011;

B.0110;

C.0101;

D.0100

第8题:

在单译码结构中,地址输入线n=4,经地址译码器译码,可译出( )个状态。

A.4

B.12

C.16

D.20

第9题:

阅读以下关于输入输出接口设计的说明,回答问题1至问题3,将解答填入对应栏内。

【说明】

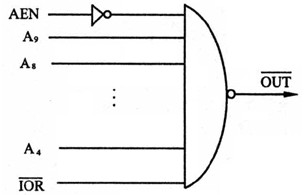

下图为采用查询方式工作的输入接口,地址译码器中A15~A1直接接到或门的输入端。

输入设备在向接口传送8位数据的同时,还传送负脉冲STB,该信号的作用是什么?

脉冲除了将输入设备的数据锁存到锁存器的输出端外该脉冲还用来触发D触发器使其输出Q为高电平此高电平表示外设有数据准备好。

脉冲除了将输入设备的数据锁存到锁存器的输出端外该脉冲还用来触发D触发器使其输出Q为高电平此高电平表示外设有数据准备好。 脉冲除了将输入设备的数据锁存到锁存器的输出端外,该脉冲还用来触发D触发器,使其输出Q为高电平,此高电平表示外设有数据准备好。 解析:本题考查输入输出接口设计以及输入输出控制方式应用知识。

脉冲除了将输入设备的数据锁存到锁存器的输出端外,该脉冲还用来触发D触发器,使其输出Q为高电平,此高电平表示外设有数据准备好。 解析:本题考查输入输出接口设计以及输入输出控制方式应用知识。计算机与外设之间进行数据传送主要有三种基本控制方式:查询方式、中断方式和DMA方式。

查询方式是通过执行输入/输出查询程序来完成数据传送的,其工作原理是:当CPU。启动外设工作后,不断地读取外设的状态信息进行测试,查询外设是否准备就绪,如外设准备好,则可以进行数据传送:否则,CPU继续读取外设的状态信息进行查询等待,直到外设准备好。

采用程序查询方式进行数据传送时,实际上在外设准备就绪之前,CPU一直处于等待状态,致使CPU的利用率较低。倘若CPU按这种方式与多个外设传送数据时,就需要周期性的依次查询每个外设的状态,浪费的时间就更多,CPU的利用率就更低。因此,这种方式适合于工作不太繁忙的系统。

中断方式是一种硬件和软件相结合的技术,中断请求和处理依赖于中断控制逻辑,而数据传送则是通过执行中断服务程序来实现的。这种方式的特点是:在外设工作期间,CPU无须等待,可以处理其他任务,CPU与外设可以并行工作,提高了系统效率,同时又能满足实时信息处理的需要。但在进行数据传送时,仍需要通过执行程序来完成。

采用中断方式可以提高CPU的利用率,但有些I/O设备(如磁盘、光盘等)需要高速而又频繁地与存储器进行批量的数据交换,此时中断方式已不能满足速度上的要求。而直接存储器处理DMA方式,可以在存储器与外设之间开辟一条高速数据通道,使外设与存储器之间可以直接进行批量数据传送。实现DMA传送,要求CPU让出系统总线的控制权,然后由专用硬件设备(DMA控制器)来控制外设与存储器之间的数据传送。这种传送方式的特点是:在数据传送过程中,由DMA控制器参与工作,不需要CPU的干预,批量数据传送时效率很高,通常用于高速I/O设备与内存之间的数据传送。

本题采用程序查询方式从输入设备读取数据。

接口图中的选通信号

低电平有效,是由外设提供的输入信号。当该信号有效时,将输入设备送来的数据锁存至输入锁存器中临时存储起来,并设置数据已经准备好的状态,标志该状态的是上图中的D触发器。

低电平有效,是由外设提供的输入信号。当该信号有效时,将输入设备送来的数据锁存至输入锁存器中临时存储起来,并设置数据已经准备好的状态,标志该状态的是上图中的D触发器。D触发器的初始状态为0(数据未准备好),当输入设备的数据准备好时,通过CP将D触发器设置为1,标明数据已准备好,CPU可随时读取。

要从输入设备读取数据(

有效),首先应确定输入设备的端口地址,包括状态端口和数据端口。从题图中可知,要读取输入设备的状态端口(即数据是否准备好),需进行下面的运算:

有效),首先应确定输入设备的端口地址,包括状态端口和数据端口。从题图中可知,要读取输入设备的状态端口(即数据是否准备好),需进行下面的运算:A15+A14+A13+…+A2+A1+

+

+

即地址信号A15、A14、…、A2、A1与IOR进行或运算(经过或门)后的输出,与A0经非门后的输出再进行或运算,若为0,则可将D触发器中的状态输出至数据线D7,因此,要求A15、A14、…、A2、A1全部为0且A0为1,即状态端口地址为0001H。同理,要读取输入设备的数据,需进行下面的运算:

A15+A14+A13+…+A2+A1+

+A0

+A0即当A15、A14、…、A2、A1全部为0并且A0也为0,才能通过三态门将数据送往数据总线,因此数据端口地址为0000H。

若用查询方式将输入设备的一个数据读入CPU的BL寄存器中,则根据其工作方式,需要对I/O接口的状态不断进行测试,一旦满足条件(准备好传送数据即外设就绪),紧接着就执行数据传送指令,程序如下:

START: MOVDX,0001H;外设的状态端口号送入DX寄存器

NEXT1: IN AL,DX ;从外设端口读取状态并暂存入AL

NEXT2: ANDAL,80H;判断数据是否就绪(D7是否为1)

JZ NEXT1;未就绪(D7为0),则继续查询,否则开始读取数据

MOVDX, 0000H ;外设数据端口号送入DX寄存器

IN AL,DX ;从外设端口读取数据到的数据暂存入AL

NEXT3: MOVBL,AL ;将数据送入BL寄存器

RET

第10题:

欲使图中地址译码器的输入信号有效,其中的控制信号AEN和IOR必须分别取值为______,______。

0,1