某机字长16位,CPU地址总线18位,数据总线16位,存储器按字编址,CPU的控制信号线有:MREQ#(存储器访问请求,低电平有效),R/W#(读写控制,低电平为写信号,高电平为读信号)。试问:【**,★,包捷5.2,编号3.3,3.5.2】 该机可以配备的最大主存容量为()。

题目

某机字长16位,CPU地址总线18位,数据总线16位,存储器按字编址,CPU的控制信号线有:MREQ#(存储器访问请求,低电平有效),R/W#(读写控制,低电平为写信号,高电平为读信号)。试问:【**,★,包捷5.2,编号3.3,3.5.2】 该机可以配备的最大主存容量为()。

相似问题和答案

第1题:

在使用PCI总线的奔腾计算机中,CPU访问(读写)主存储器通过( )总线进行。

A.ISA总线(AT总线)

B.PCI总线

C.VESA 总线

D.CPU—存储器总线

请帮忙给出正确答案和分析,谢谢!

第2题:

80386有4个总线周期定义信号,分别为W/R、D/C、M/IO和LOCK;其中前3个是主要的总线周期定义信号在存储器数据读取周期,各总线周期定义信号为( )。

A.W/R=L低电平,D/C=H高电平,M/IO=H高电平

B.W/R=L低电平,D/C=H高电平,M/IO=L低电平

C.W/R=H高电平,D/C=L低电平,M/IO=H高电平

D.W/R=L低电平,D/C=L低电平,M/IO=H高电平

第3题:

A.以“字”为单位进行编址的

B.是中央处理机能够直接访问的惟一的存储空间

C.与辅助存储器相比速度快、容量大、价格低的一类存储器

D.只能被CPU访问的存储器

第4题:

B.512

C.64

D.128

第5题:

80386有4个总线周期定义信号分别为W/R、D/C、M/IO和LOCK,其中前3个是主要的总线周期定义信号,在FO写周期,各总线周期定义信号为( )。

A.W/R=L低电平,D/C=H高电平,M/IO=H高电平

B.W/R=L低电平,D/C=H高电平,M/IO=L低电平

C.W/R=H高电平,D/C=L低电平,M/IO=H高电平

D.W/R=L低电平,D/C=L低电平,M/IO=H高电平

第6题:

计算机的总线包含了地址总线,数据总线和控制总线。某计算机CPU有16条地址总线,则该计算机最大的寻址空间为(2)字节,若该CPU寻址外部的数据存储器时,第16条地址线始终为高电平,则此数据存储器的地址空间为(3)字节。

A.32k

B.48k

C.64k

D.128k

解析:在计算机中,地址线为N条,则最大寻地址空间为2NB。答案为C。

第7题:

在使用PCI总线的微型计算机中,CPU访问(读/写)主存储器通过下列( )进行。

A.ISA总线(AT总线)

B.PCI总线

C.VESA总线

D.CPU存储器总线

第8题:

A、存储器的访问速度

B、CPU可直接访问的存储器空间大小

C、存储器的字长

D、存储器的稳定性

答案:B

解析:计算机中,地址总线的宽度决定了CPU能够访问的物理地址空间的大小。

第9题:

C.U盘

D.磁盘

第10题:

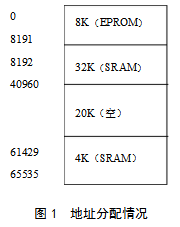

CPU的地址总线16根(A15~A0,A0是低位),双向数据总线16根(D15~D0),控制总线中与主存有关的信号 有!MREQ(允许访存,低电平有效),R/!W(高电平读命令,低电平写命令)。主存地址空间分配如下:0~8191为系统程序区,由EPROM芯片组成,从8192起一共32K地址空间为用户程序区,最后(最大地址)4K地址空间为系统程序工作区。如图1所示。上述地址为十进制,按字编址。现有如下芯片。 EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,4K×16位,8K×16位 请从上述芯片中选择芯片设计该计算机的主存储器,画出主存逻辑框图。

EPROM:8K×16位(控制端仅有!CS),16位×8位 SRAM:16K×1位,2K×8位,4K×16位,8K×16位 请从上述芯片中选择芯片设计该计算机的主存储器,画出主存逻辑框图。

略