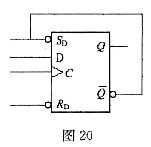

用3个D触发器组成的电路如图7-69所示,触发器F0的输入端接+5V表明D0=1,那么,在第1个CP脉冲和第2个脉冲的上升沿过后Q2Q1Q0分别是()。A、101和011B、011和111C、001和011D、000和111

题目

用3个D触发器组成的电路如图7-69所示,触发器F0的输入端接+5V表明D0=1,那么,在第1个CP脉冲和第2个脉冲的上升沿过后Q2Q1Q0分别是()。

- A、101和011

- B、011和111

- C、001和011

- D、000和111

参考答案和解析

相似问题和答案

第1题:

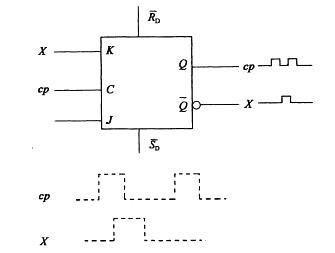

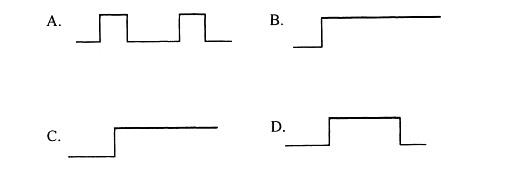

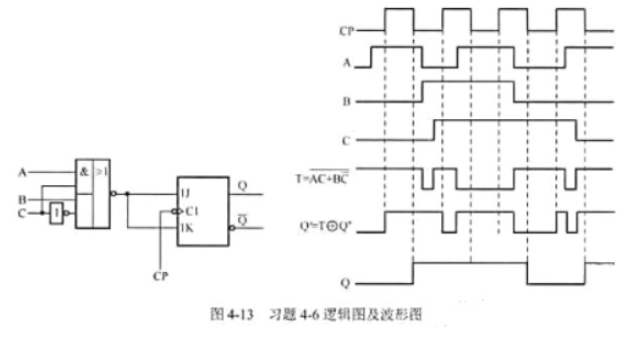

试分别画出图4-30(a)电路输出端Y、Z和图4-30(b)电路输出端Q2的波形.输入信号A和CP的电压波形如图4-30(c)所示,各触发器的初始状态为0.

第2题:

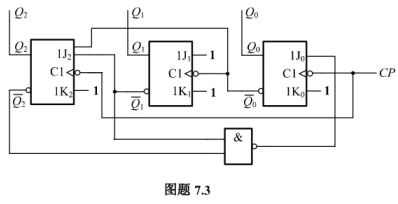

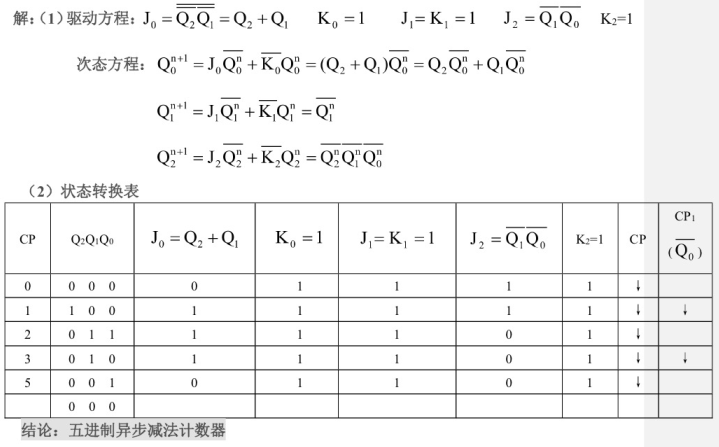

计数器电路如图题7.3所示。设各触发器的初始状态均为“0”,要求:

(1) 写出各触发器的驱动方程和次态方程;

(2)画出次态卡诺图;画出状态转换图并说明该计数器电路的逻辑功能;

第3题:

A、D

B、T

C、RS

D、Tˊ

第4题:

B、置1

C、计数

D、置0

第5题:

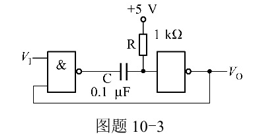

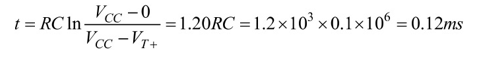

CMOS 门组成的微分型单稳态触发器如图题10-3 所示。若电阻R=1kΩ,电

容C=0.1μF,试计算该电路的暂稳态时间。

第6题:

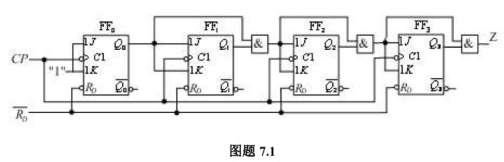

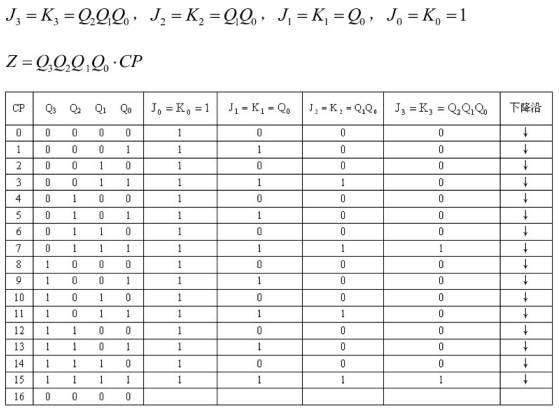

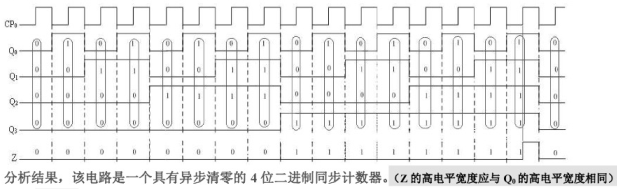

计数器电路如图题7.1所示。设各触发器的初始状态均为“0”,分析该电路的逻辑功能。

由状态转换表,可以绘制出逻辑波形图

由状态转换表,可以绘制出逻辑波形图

第7题:

试画出图题5-19所示电路中触发器输出Q1、Q2端的波形,输入端CLK的波形如图所示。(设Q初始状态为0)

第8题:

第9题:

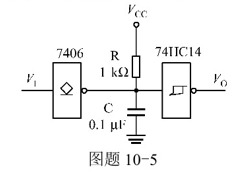

由门电路 7406、74HC14组成的积分型单稳态触发器如图题10-5所示。若电阻R=10kΩ、电容C=0.1μF,试计算该电路的暂稳态时间。

第10题: