某计算机字长为32位,存储器存取周期为100ns,则存储器的带宽为(10);若CPU执行一段程序,访问存储器1600次,访问cache400次(cache的存储周期为50s),则平均访问存储器的时间为(11)。(63)A.32×106bit/sB.32×107bit/sC.107bit/sD.3200bit/s

题目

某计算机字长为32位,存储器存取周期为100ns,则存储器的带宽为(10);若CPU执行一段程序,访问存储器1600次,访问cache400次(cache的存储周期为50s),则平均访问存储器的时间为(11)。

(63)

A.32×106bit/s

B.32×107bit/s

C.107bit/s

D.3200bit/s

相似问题和答案

第1题:

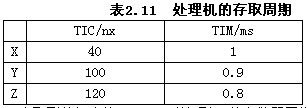

设有三个指令系统相同的处理机X、Y和乙它们都有4KB的高速缓冲存储器和 32 MB的内存,但是其存取周期都不一样,如表2.11所示(TIC和TIM分别表示I处理机 Cahce存取周期和主存存取周期)。

若某段程序所需指令或数据在Cache中取到的概率为P=0.5,则处理机X的存储器平均存取周期为(50)ms。假定指令执行时间与存储器的平均存取周期成正比,此时三个处理机执行该段程序由快到慢的顺序为(51)。

若P=0.65,则顺序为(52)。

若P=0.8,则顺序为(53)。

若P=0.85,则顺序为(54)。

A.0.2

B.0.48

C.0.52

D.0.6

解析:平均存取周期=Cache存取周期×Cache命中率+主存存取周期×Cache失效率=(0.5×0.04ms+0.5×1ms)=520ns依此类推,因为执行速度与存取周期(执行时间)成反比,因此在Cache命中率分别为0.5、0.65、0.8、0.85的条件下,三个处理机执行该段程序由快到慢的顺序分别为:Z、Y、X,Z、X、Y,X、Z、Y,X、Y、Z。

第2题:

在CPU执行一段程序的过程中,Cache的存取次数为4600次,由主存完成的存取次数为400次。若Cache的存取周期为5ns,主存的存取周期为25ns,则CPU的平均访问时间为______ns。

A.5.4

B.6.6

C.8.8

D.9.2

解析:在CPU执行一段程序的过程中,Cache的存取次数为4600次,由主存完成的存取次数为400次。Cache的命中率Hc=4600/(4600+400)=0.92。若Cache的存取周期Tc=5ns,主存的存取周期Tm=25ns,则CPU的平均访问时间Ta为:Ta=Hc.Tc+(1-Hc).Tm=0.92×5+(1-0.92)×25=6.6ns

第3题:

某存储器数据总线宽度为32bit,存取周期为250ns,则该存储器带宽为(26)。(注:本题答案中的B表示Byte)

A.8×106B/s

B.16×106B/s

C.16×108B/s

D.32×106B/s

解析:本题考查嵌入式存储体系的基础知识。存储带宽指每秒钟能够存储的数据量。由于存储周期为250ns,就是说每250ns执行一次存储操作,即每秒钟执行4×106次存储操作。由于存储器数据总线宽度为32bit,也就是每次存储数据32/8=4B。所以该存储器带宽为4×106×4=16×106B/s。

第4题:

假设某计算机具有1 MB的内存(目前使用的计算机往往具有128 MB以上的内存),并按字节编址,为了能存取该内存各地址的内容,其地址寄存器至少需要二进制(42)位。为了使4字节组成的字能从存储器中一次读出,要求存放在存储器中的字边界对齐,1字节的地址码应(43)。若存储器周期为200ns,且每个周期可访问4字节,则该存储器带宽为(44)b/s。假如程序员可用的存储空间为4MB,则程序员所用的地址为(45),而真正访问内存的地址称为(46)。

A.10

B.16

C.20

D.32

第5题:

某计算机的存储系统由Cache-主存系统构成,Cache的存取周期为10ns,主存的存取周期为50ns。在CPU执行一段程序时,Cache完成存取的次数为4800次,主存完成存取的次数为200次,则CPU访问存储系统的平均访问时间是(30)ns,该Cache-主存系统的效率是(31)。

A.10

B.11.60

C.11.68

D.50

解析:在由Cache-主存系统构成计算机中,存储系统Cache的命中率可以计算为:

H=4800÷(4800+200)=0.96

CPU访问存储系统的平均访问时间是:

T=10×0.96+(1-0.96)50=11.6

Cache-主存系统的效率为:

e=10/11.6=0.862

第6题:

在CPU和主存间设置cache存储器主要是为了(14)。若使用基于数据内容进行访问的存储设备作为cache时,能更快决定是否命中。这种地址映射方法称为(15)映射。CPU向cache执行写操作时,可以同时写回主存储器或者仅当cache中该数据被淘汰时才写回主存储器,前者称为(16),而后者称为(17)。若cache的存取速度是主存存取速度的10倍,且命中率可达到0.8,则CPU对该存储系统的平均存取周期为(18)T(T为主有的存取周期)。

A.扩充主存容量

B.解决CPU和主存的速度匹配

C.提高可靠性

D.增加CPU访问的并行度

第7题:

假设某计算机有1MB的内存,并按字节编址,为了能存取其中的内容,其地址寄存器至少需要(9)位。为使4字节组成的字能从存储器中一次读出,要求存放在存储器中的字边界对齐,一个字的地址码应(10)。若存储周期为200ns,且每个周期访问 4B,则该存储器的带宽为(11)bit/s。假如程序员可用的存储空间为4MB,则程序员所用的地址为(12),而真正访问内存的地址为(13)。

A.10

B.16

C.20

D.32

第8题:

CPU直接访问的存储器是()。

A、软盘

B、硬盘

C、只读存储器

D、随机存取存储器

第9题:

如存储器的工作频率为333MHz,数据线宽度为32位,每个周期传输1次数据,则存储器的带宽=___【23】____MB/s。若存储器总线采用串行总线,以10位为一个数据帧(包含一个字节的存储数据),则总线带宽=总线频率/___【24】____。

第10题:

在CPU执行一段程序的过程中,cache的存取次数为3800次,由主存完成的存取次数为200次。若cache的存取周期为5ns,主存的存取周期为25ns,则cache的命中率为(1);CPU的平均访问时间为(2)ns。

A.0.93

B.0.95

C.0.97

D.0.99

解析:命中率(hit rate)可以简单地定义为在cache存储器(M1)中访问到的概率。选择一组有代表性的程序,在程序执行过程中分别统计对M1存储器的访问次数N1和对主存储(M2)的访问次数N2,则h=N1/(N1+N2)。因此,题中cache的命中率可以这样计算 3800/(3800+200)=0.95。如果以h代表对cache的访问命中率,t1表示cache的周期时间。t2表示主存储器周期时间。以读操作为例,设“cache+主存储器”的系统的平均周期为t3则:t3=h×t1 +(1-h)×t2。其中,(1-h)又称为失效率(未命中率,miss rate)。因此,题中的CPU的平均访问时间,可以这样计算0.95×5+(1-0.95)×25=6。