单选题异步方式下,825lA的时钟CLK比数据传输率大()倍。A 4.5B 330C 15D 25

题目

4.5

330

15

25

相似问题和答案

第1题:

在传输率相同的情况下,同步串行通信的字符信息传输率一定比异步串行通信的高。()

第2题:

Intel 825lA可以工作在( )。

A.同步方式

B.异步方式

C.全双工方式

D.以上都对

第3题:

A.if clk’event and clk = ‘1’ then

B.if falling_edge(clk) then

C.if clk’event and clk = ‘0’ then

D.if clk’stable and not clk = ‘1’ then

第4题:

什么是clk时钟信号?

正确答案: 提供给移位寄存器的移位脉冲,每一个脉冲将引起数据移入或移出一位。数据口上的数据必须与时钟信号协调才能正常传送数据,数据信号的频率必须是时钟信号的频率的1/2倍。在任何情况下,当时钟信号有异常时,会使整板显示杂乱无章。

第5题:

在GSM手机电路中,“M-CLK”一般表示()

- A、主时钟

- B、显示时钟

- C、频率合成时钟

- D、卡时钟

正确答案:A

第6题:

写异步D触发器的verilog module。(扬智电子笔试)

module dff8(clk , reset, d, q);

input clk;

input reset;

input [7:0] d;

output [7:0] q;

reg [7:0] q;

always @ (posedge clk or posedge reset)

if(reset)

q <= 0;

else

q <= d;

endmodule

第7题:

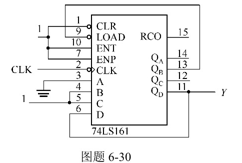

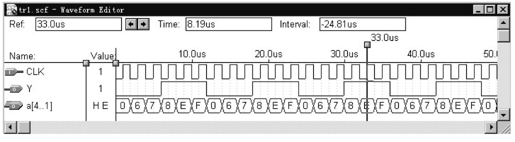

试画出图题6-30所示电路的状态图,并画出时钟CLK作用下的Y端波形。

第8题:

在数据传输率相同的情况下,同步传输的字符传送速度高于异步传输的字符传送速度,其原因是

A.同步传输采用了中断方式

B.同步传输中所附加的冗余信息量少

C.同步传输中发送时钟和接收时钟严格一致

D.同步传输采用了检错能力强的CRC校验

第9题:

异步方式下,825lA的时钟CLK比数据传输率大()倍。

- A、4.5

- B、330

- C、15

- D、25

正确答案:A

第10题:

外部CLK2的频率是80386内部时钟信号频率的()倍。

- A、5

- B、4

- C、3

- D、2

正确答案:D