单选题在处理器上的Cache是什么Cache()。A L1 CacheB 动态 CacheC 处理增加 CacheD RAM CacheE 系统 Cache

题目

L1 Cache

动态 Cache

处理增加 Cache

RAM Cache

系统 Cache

相似问题和答案

第1题:

以下关于Cache(高速缓冲存储器)的描述,(9)是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是主存部分内容的拷贝

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

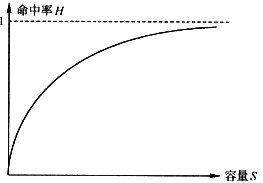

解析:本题考查高速缓存基础知识。高速缓存Cache有如下特点:它位于CPU和主存之间,由硬件实现;容量小,一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器制成;其内容是主存内容的副本,对程序员来说是透明的;Cache既可存放程序又可存放数据。Cache存储器用来存放主存的部分拷贝(副本)。控制部分的功能是:判断CPU要访问的信息是否在Cache存储器中,若在即为命中,若不在则没有命中。命中时直接对 Cache存储器寻址。未命中时,若是读取操作,则从主存中读取数据,并按照确定的替换原则把该数据写入Cache存储器中:若是写入操作,则将数据写入主存即可。Cache的命中率主要与如下几个因素有关:程序在执行过程中的地址流分布情况;当发生Cache块失效时,所采用的替换算法;Cache的容量;在组相联映像方式中,块的大小和分组的数目;所采用的Cache预取算法等。Cache的命中率随其容量增加而提高,它们之间的关系曲线如下图所示。在Cache容量比较小的时候,命中率提高的非常快,随着Cache容量的增加,命中率提高的速度逐渐降低。当Cache容量增加到无穷大时,命中率可望达到100%,但这实际上是做不到的。

第2题:

Pentium 4微处理器的L1 Cache包括两个部分,它们是指令Cache(ETC) Cache。

数据

第3题:

●下面是关于CPU与主存储器之间的Cache的叙述,其中正确的是 (43) 。

(43) A.Cache存放的只是主存储器中某一部分内容的映象

B.Cache能由用户直接访问

C.位于主板上的L2 Cache要比与CPU封装在一起的L2 Cache速度快

D.位于主板上的L2 Cache要比与CPU做在一基片上的L2 Cache速度快

【解析】Cache负责解决主存与CPU之间速度的协调问题。Cache中存放着主存的一部分副本(主存中的部分内容),不能由用户直接访问。Cache可以有多级,离CPU越近的,速度越快。

第4题:

B.4,12,16

C.5,10,17

D.5,12,15

第5题:

A 主频

B 字长

C 存取周期

D Cache 容量

第6题:

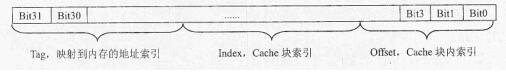

在嵌入式处理器中,CACHE的主要功能由(29)实现;某32位计算机的CACHE容量为16KB(B:字节),CACHE块的大小为16B(B:字节),若主存与CACHE地址映像采用直接映像方式,则主存地址为0x1234E8F8的单元装入CACHE的地址(30);在下列CACHE替换算法中,平均命中率最高的是(31)。

A.硬件

B.软件

C.操作系统

D.应用程序

第7题:

下面关于Cache的叙述,“(6)”是错误的。

A.在体系结构上,Cache存储器位于主存与CPU之间

B.Cache存储器存储的内容是动态更新的

C.使用Cache存储器并不能扩大主存的容量

D.Cache的命中率只与其容量相关

解析:本题考查高速缓存基础知识。高速缓存Cache有如下特点:它位于CPU和主存之间,由硬件实现;容量小,一般在几KB到几MB之间;速度一般比主存快5到10倍,由快速半导体存储器制成;其内容是主存内容的副本,对程序员来说是透明的;Cache既可存放程序又可存放数据。Cache存储器用来动态存放主存的部分拷贝(副本)。控制部分的功能是:判断CPU要访问的信息是否在Cache存储器中,若在即为命中,若不在则没有命中。命中时直接对Cache存储器寻址。未命中时,若是读取操作,则从主存中读取数据,并按照确定的替换原则把该数据写入Cache存储器中:若是写入操作,则将数据写入主存即可。Cache的命中率主要与如下几个因素有关:程序在执行过程中的地址流分布情况;当发生Cache块失效时,所采用的替换算法;Cache的容量;在组相联映像方式中,块的大小和分组的数目;所采用的Cache预取算法等等。Cache的命中率随其容量增加而提高,它们之间的关系曲线如下图所示。在Cache容量比较小的时候,命中率提高的非常快,随着Cache容量的增加,命中率提高的速度逐渐降低。当Cache容量增加到无穷大时,命中率可望达到100%,但这是实际上是做不到的。

第8题:

下面是微处理器中有关Cache的叙述,其中错误的是

A.从Pentium微处理器开始已经将其内部的L1 Cache分离为指令Cache和数据Cache

B.Pentium Ⅱ的L2 Cache不在微处理器芯片内部

C.Pentium 4微处理器的L1 Cache和L2 Cache均集成在处理器芯片内

D.目前市场上销售的赛扬(Celeron)微处理器价格较低,因为芯片内部没有集成Cache

解析:该题考查考生对微处理器Cache的理解。Pentium微处理器中将原来的数据和指令混合使用的8KB Cache分成两个独立的双路相联的8KB指令Cache和8KB数据Cache,从而减少了等待和传输数据的次数和时间,提高了芯片的整体性能,所以选项A是正确的;为了进一步提高微处理器的性能,除了原有的片内L1 Cache以外,还增加了L2 Cache,其中Pentium Ⅱ的L2 Cache不在微处理器芯片内部,而是在片外电路中,并有全速总线与CPU紧密连接,所以选项B是正确的; Pentium 4檄处理器的L1 Cache和L2 Cache均集成在处理器芯片内,而且所使用的Cache速度比 Pentium 3的Cache快1.8倍,所以选项C是正确的;赛扬(Celeron)微处理器不是没有Cache,而只是没有512KB的L2 Cache,故D错,所以应该选择D。

第9题:

A.L1 Cache

B.动态 Cache

C.处理增加 Cache

D.RAM Cache

E.系统 Cache

第10题:

如果应用程序需要的数据已经在内存中,称作()。

- A、Cache Read

- B、Cache Hit

- C、Cache Miss

- D、Cache Latch

正确答案:B